在线时间22 小时

UID3154085

注册时间2015-8-3

NXP金币0

该用户从未签到

中级会员

- 积分

- 277

- 最后登录

- 2020-2-24

|

楼主 |

发表于 2015-8-19 08:57:37

|

显示全部楼层

哈哈,不是波特率发生器的问题~

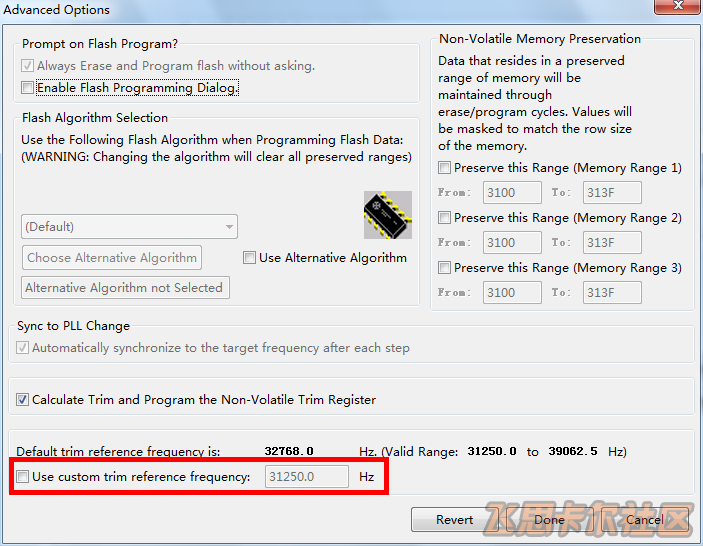

我昨天在ICS设置为FEI时,用定时器测试了下总线频率,发现总线频率快了5%,原因是我想用31250的内部时钟产生16Mhz的CLKout,但是DebugSetting那边没有将Trim值改成31250,还是默认的32768,所以ICS_C3的值错了,刚好快了4.8%。说到这,问题来了,我这个工程是用PE生成的,我设置时钟的时候,PE怎么没有帮我把这个改一下,连个错误提示都没有?

DebugSetting

另外,我用PE生成的代码ICS设置成FBELP模式,也必须要把这个内部时钟设置为31250,系统频率才能准确。

想请教下各位,我想选外部晶振(16MHz)做时钟源的话应该怎么设置?

我看规格书上的FBE的例子,需要有个等待的while,但是我按这种方法设置后,程序根本运行不过去。

而PE生成的FBELP的初始化代码和这个又不一样,没有这个等待。

- Example: 8.3.4.1 FBE mode initialization routine

- /* the following code segment demonstrates setting ICS to FBE mode generating 20MHZ bus*/

- /* supposing external 20MHZ crystal is installed in high gain mode */

- ICS_OSCSC = 0x96; /* high-range, high-gain, oscillator required */

- <b>while (ICS_OSCINIT == 0); /* waiting until oscillator is ready *///程序执行到这会死循环。</b>

- ICS_C1 = 0x80; /* external clock reference (20MHZ) to FLL output */

- ICS_C2 = 0x00; /* BDIV = 0, prescalar = 1 */

|

|

/4

/4