在线时间104 小时

UID3338547

注册时间2017-1-28

NXP金币14

TA的每日心情 | 无聊

2021-12-29 19:06 |

|---|

签到天数: 47 天 连续签到: 1 天 [LV.5]常住居民I

金牌会员

- 积分

- 1392

- 最后登录

- 2025-3-4

|

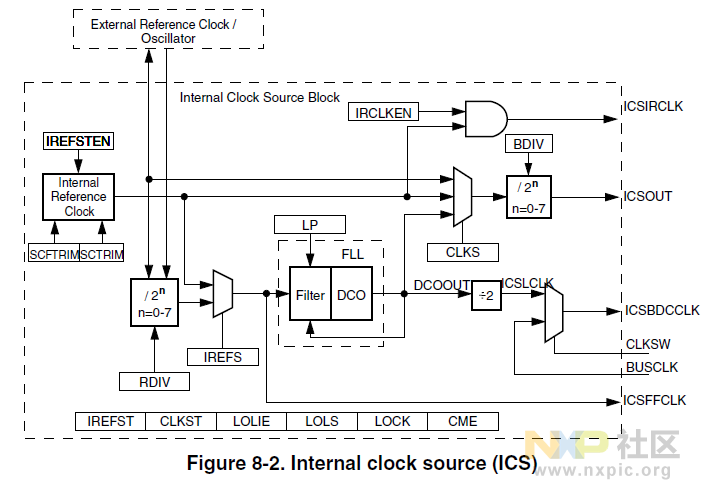

时钟框图

老实说这个框图不是很好看,甚至连时钟源都看不出来,数据手册上有另外一个框图:

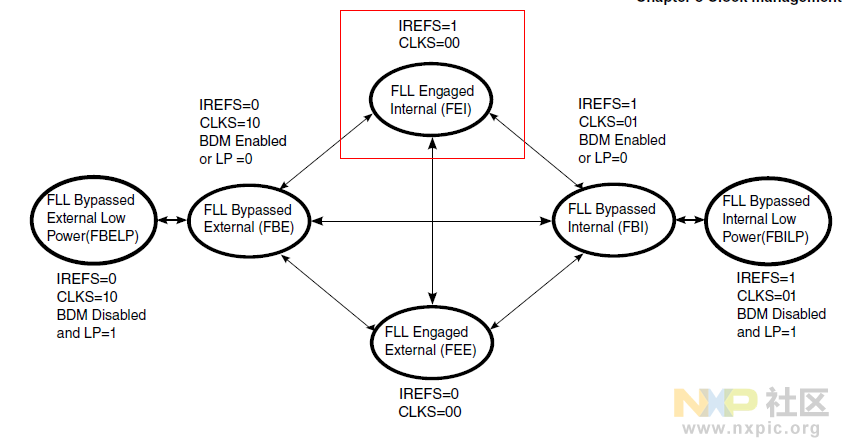

图中可以看到,一共有六个时钟源

FEI, FEE, FBI, FBI, FBE, FBE

其中F代表FLL

B代表bypassed

E代表Engaged

I代表内部时钟

第二个E代表外部时钟

倍频与Engaged

Engaged代表这个时钟会倍频。

从何找到依据呢?

我们可以看第一张图FLL那个位置,有一个虚框,框着两个项目:Filter、DCO

1、其中Filter就是是否选择FLL倍频(Engaged)抑或旁路掉(bypassed)FLL。

2、另一个框DCO的作用,数据手册是这样描述的:

8.2.1.5 BDC clock

The ICS presents the DCO output clock divided by two as ICSLCLK for use as a clock

source for BDC communications. ICSLCLK is not available in FLL bypassed internal

low power (FBILP) and FLL bypassed external low power (FBELP) modes. The

ICSLCLK can be selected as BDC clock.

意思大概就是经过DCO,时钟会倍频,比如原本输入是8M变成16M。

关于时钟源的选择

图中只有两个是Engaged的时钟,我们这里只讨论这两个。

1、FEI

In FLL engaged internal mode, the ICSOUT clock is derived from the FLL clock, which

is controlled by the internal reference clock.

我找遍数据手册,没有找到内部时钟的频率,根据实际配置情况,估计是4M

2、FEE

In FLL engaged external mode, the ICSOUT clock is derived from the FLL clock, which

is controlled by the external reference clock source.

以上内容包含个人主观猜测,如有疏漏,欢迎指点。

|

|

/3

/3