|

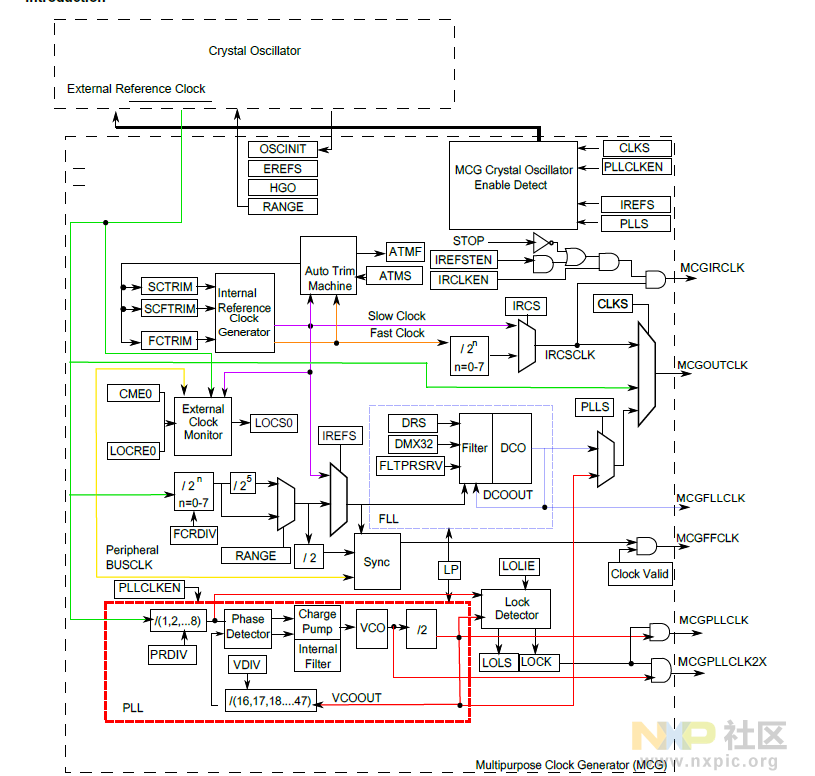

MCG--多用途时钟信号发生器,MCG模块通过对输入的参考时钟进行分频和倍频处理,可以输出各种频率的时钟信号,并达到超频运行的目的。 模块图

MCG的核心是一个FLL(锁频环)和一个PLL(锁相环)。FLL和PLL都可以对输入的参考时钟倍频并锁定后输出,输出的时钟在SIM模块的控制下提供给CPU和各个模块。

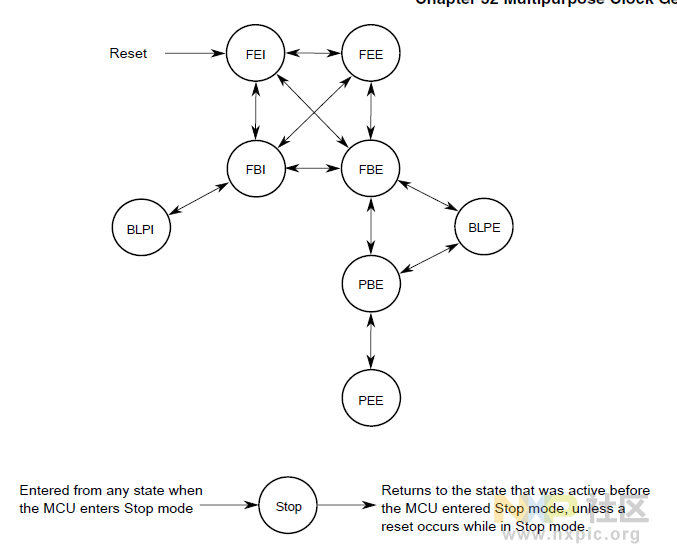

TWRKV58F220M拥有8种时钟模式,转换图如下:

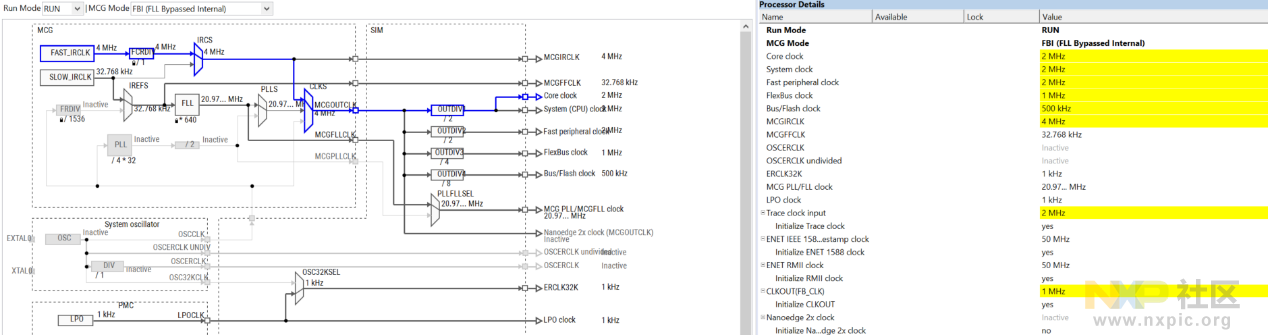

这个模块学起来是比较麻烦的。状态转换,看数据手册中不同寄存器配置都让人头大。自己去配置时钟以及时钟切换比较麻烦,MCUXpresso的configTool可以帮助我们减少麻烦,更加容易去理解时钟来源方式。 我们通过MCUXpresso来配置各种时钟模式,使用示波器查看波形。将PTC3配置为CLKOUT输出(PORT_SetPinMux(PORTC, 3U,kPORT_MuxAlt5)),来查看flexbus总线时钟频率(CLOCK_SetClkOutClock(SIM_CLKOUT_SEL_FLEXBUS_CLK);))。

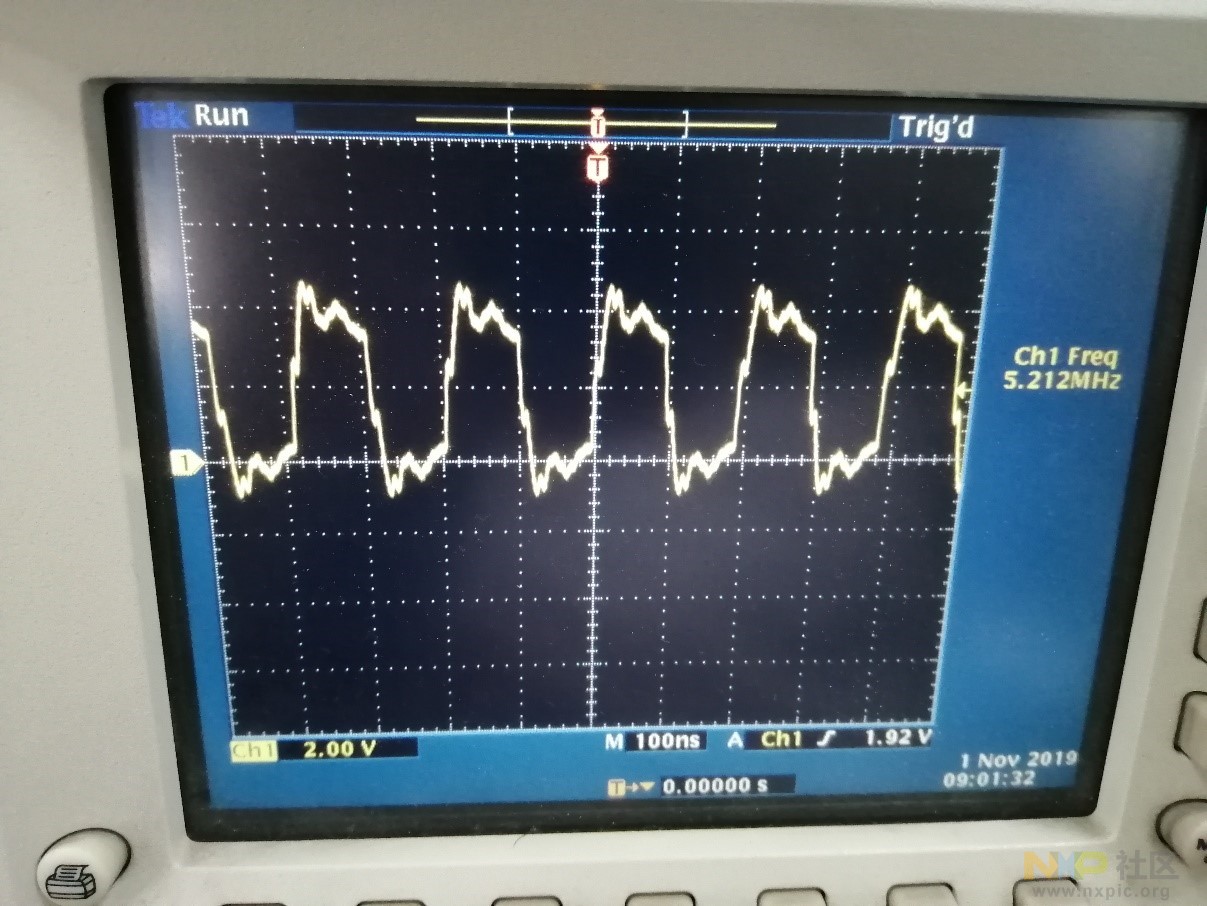

第一种FEI模式,MCU上电就进入该模式。通过蓝线可以知道该模式下,时钟的来源,我们配置core时钟为10.48576 MHz MHz,CLKOUT输出为flexbus时钟,5.24288MHz

示波器观测到的CLKOUT波形

第二种FEE, 我们配置core时钟为10 MHz,CLKOUT输出应为5MHz

示波器观测到的CLKOUT波形

第三种FBI,我们配置core时钟为2 MHz,CLKOUT输出应为1MHz

示波器观测到的CLKOUT波形

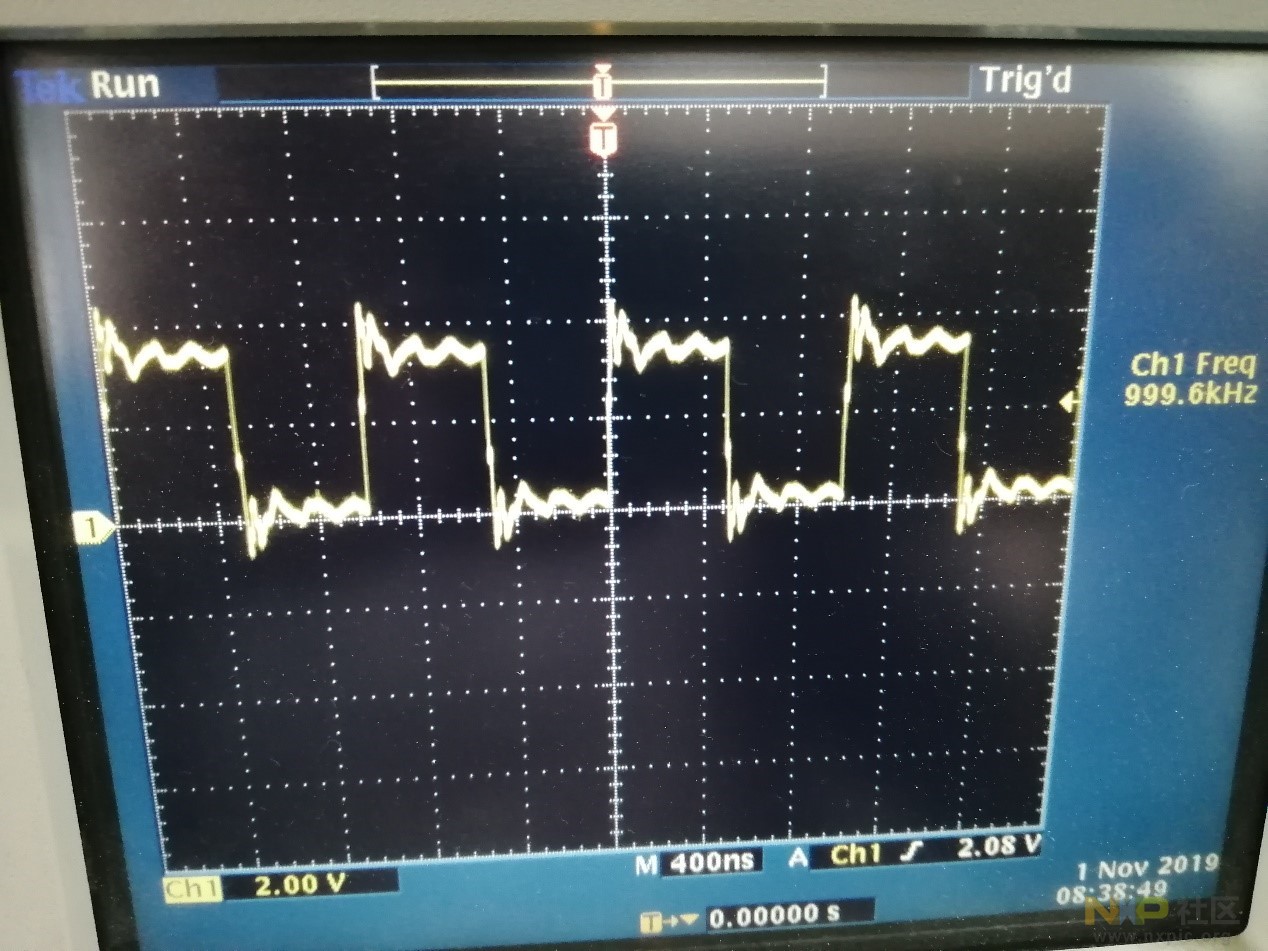

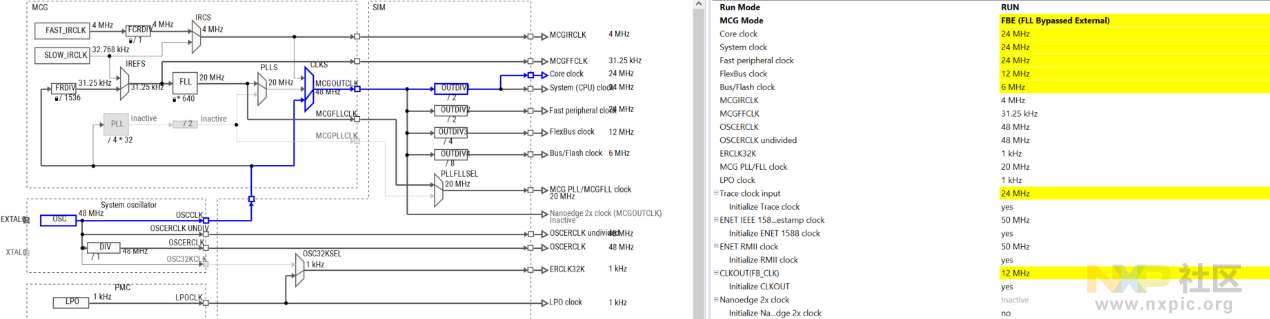

第四种FBE,我们配置core时钟为24 MHz,CLKOUT输出应为12MHz

示波器观测到的CLKOUT波形

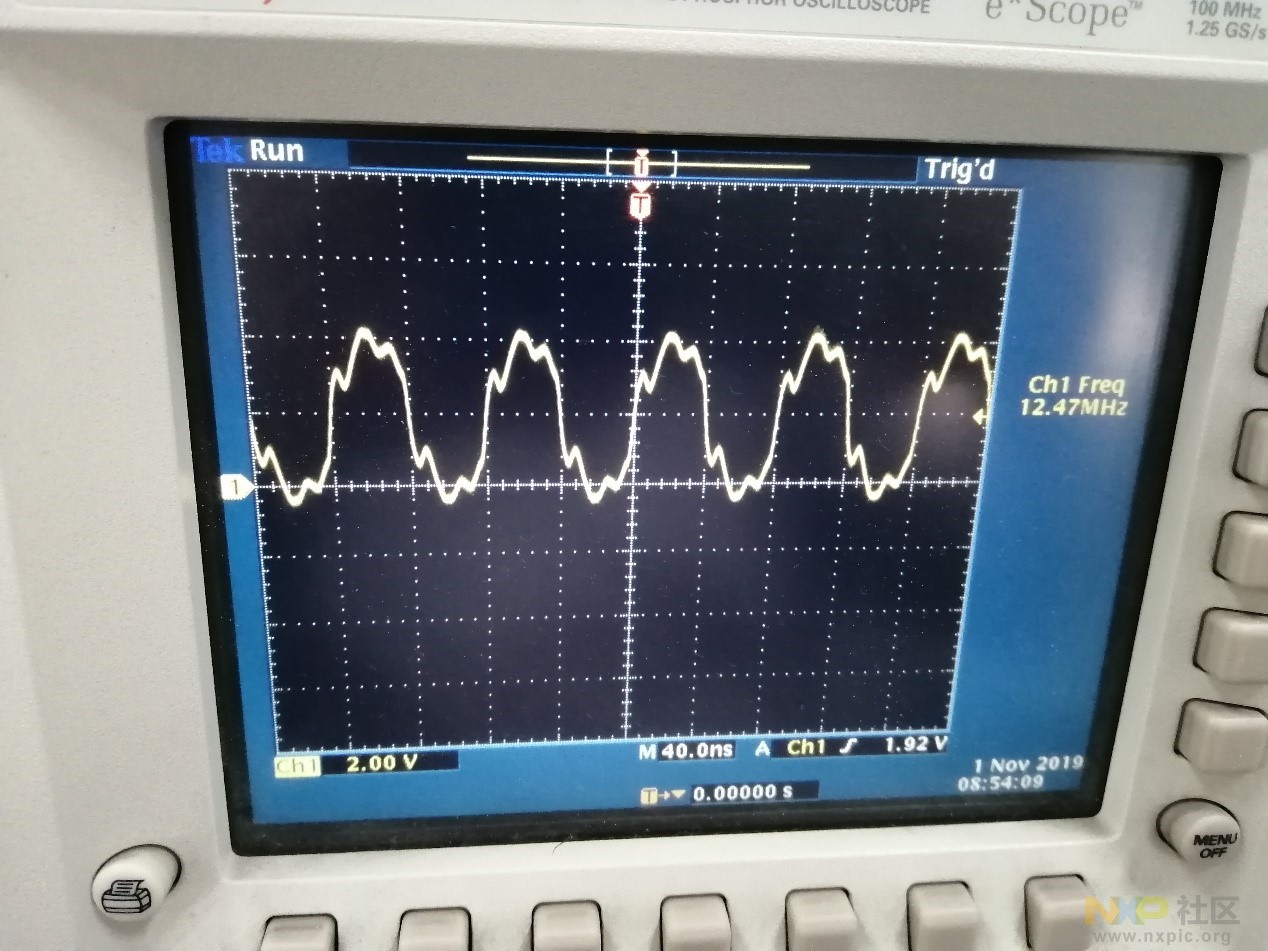

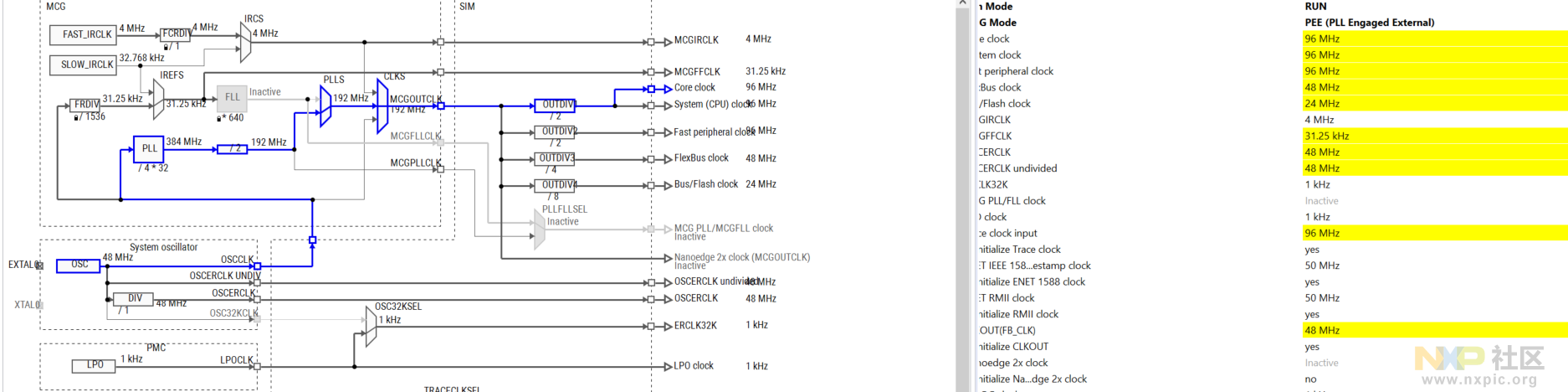

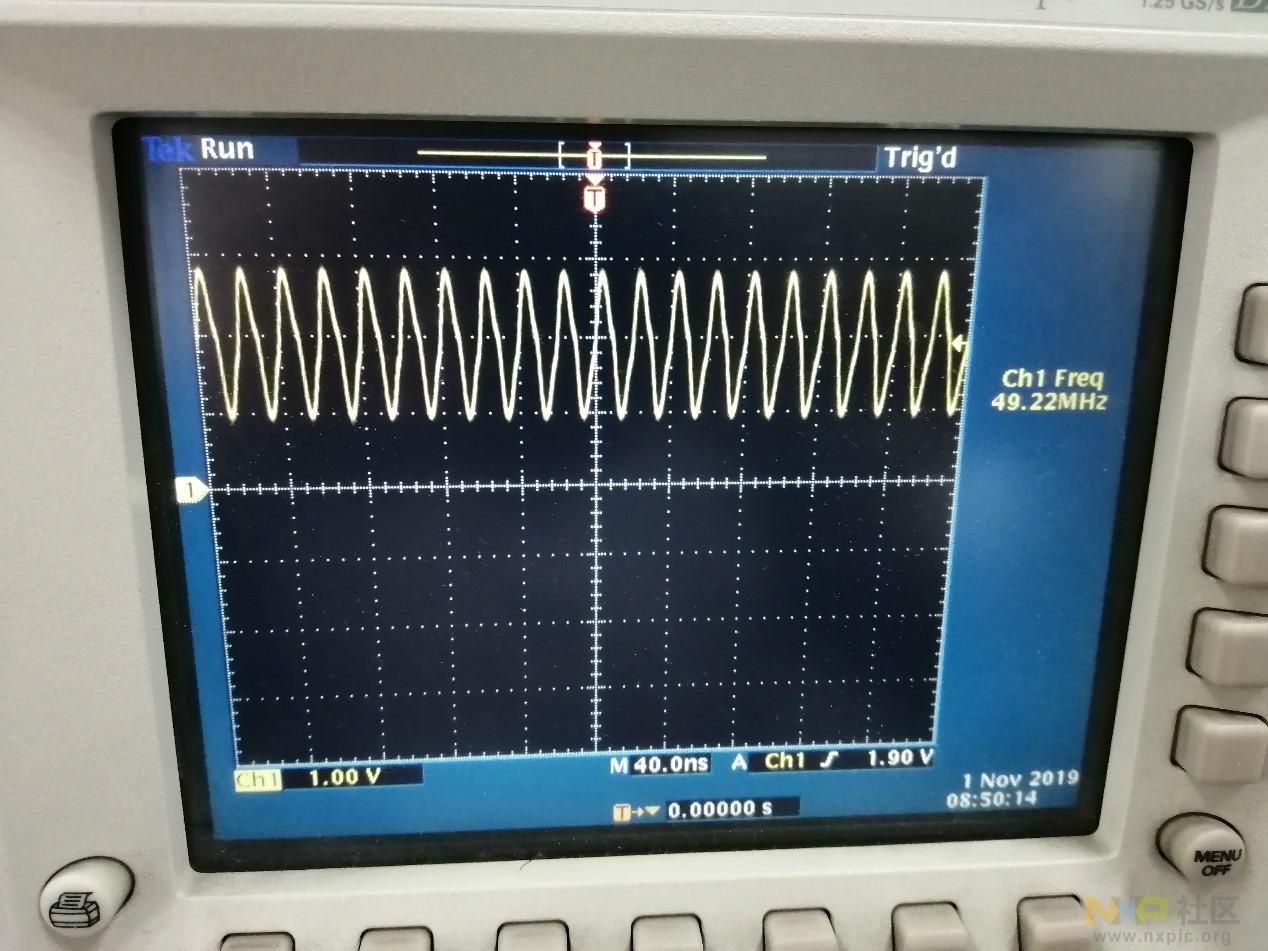

第五种PEE,我们配置core时钟为96 MHz,CLKOUT输出应为48MHz

示波器观测到的CLKOUT波形

第六种PBE,我们配置core时钟为24MHz,CLKOUT输出应为12MHz

示波器观测到的CLKOUT波形

|  /3

/3